Intel's finfets are a'complicated and difficult'technology solution,says Professor Asen Asenov of Glasgow University and founder and CEO of Gold Standard Simulations(GSS)the leading CMOS statistical variability simulation house.

"It's still not clear to me why Intel went for so complicated and difficult a technology solution,"Asenov tells EW,"SOI finfets would be much easier and better performers too."

The changing shape of Intel's finfets as reported by Chipworks and analysed by GSS has attracted a great deal of comment,says Asenov who has now published some further analyses of the Intel finfet.

Asenov's analysis starts:

'One interesting question arising from the related discussions was how much the processing-related variability in the individual fin shapes,clearly visible in Fig 7 of the Chipworks blog,will result in variability in the electrical characteristics of the individual fins,"says Asenov,"although in logic applications multiple fins are connected in parallel,resulting in averaging of their characteristics,in SRAM application the variability in the single fin characteristics is of utmost importance.'

Figure 1.TEM images of three Intel FinFETs with the GARAND simulation domain overlaid.

Asenov's analysis continues:

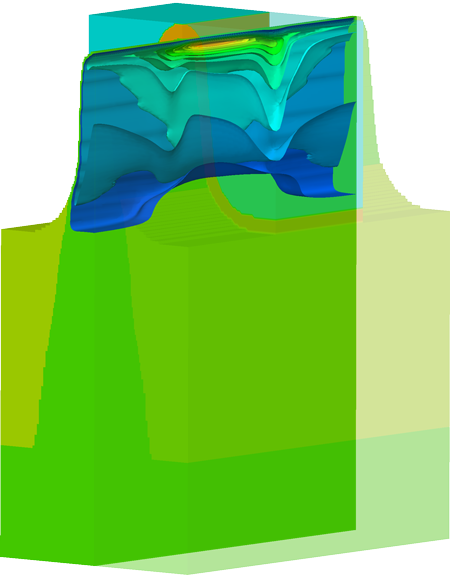

'It was fairly straightforward to introduce the different fin shapes into GARAND and the results are illustrated in Fig.1,with the simulation domain superimposed on top of the TEM image.The complex 3D shape of the simulation domain can be appreciated in full in Fig.2.

Figure 2.The 3D simulation domain for Fin 1.

Precise measurements of the FinFET dimensions were possible due to the impressive atomic resolution of the fin image in Fig.8 of the Chipworks blog,which we interpreted as shown in Fig.3.

Figure 3.Close-up of the top of one fin from a Chipworks TEM showing our estimation of the fin dimensions.

As in our previous blog,in the simulations presented here we consider that the fin itself is virtually undoped but there is a punchthrough stopper beneath the fin.Low channel doping is beneficial from the point of view of reducing the random-dopant-induced statistical variability–a well-known SRAM yield killer.

Figs.4-6 show the current density in the three fins at different gate bias conditions.The shape of each fin has a clear effect on where the current is flowing in each case.

This is further visible in Fig.7 where each fin is cut lengthwise down the centre of the fin and iso-surfaces of current density are shown.In particular,the higher current density in Fin 3 due to it having a narrower top of the fin is evident.

Figure 4.Current density across the middle of the three fins at gate voltage VG=0.0V

Figure 5.Current density across the middle of the three fins at gate voltage VG=0.3V

Figure 6.Current density across the middle of the three fins at gate voltage VG=1.0V

Figure 7.For each fin,cut lengthwise down the centre of the fin,iso-surfaces of current density are shown.VD=1.0V,VG=0.8V.

At this point you are probably keen to see the differences in the electrical characteristics of the three fins.The channel length dependence of the on-current(VG=VD=1V)of the three fins is compared in Fig.8 to the channel length dependence of the on-current of rectangular fins with 10nm and 8nm fin width and the same fin height.

Because we don't know the exact strain conditions in the Intel FinFETs we cannot guarantee the absolute value of the on-currents,but we are confident in the relative magnitudes.Surprisingly,despite significant differences in the shape of the three fins,the difference in the on-current is within a 4%range.More interestingly the rectangular fins yield approximately 12%higher on-current at comparable or better electrostatic integrity.'

Figure 8.Dependence of on-current,ION,on gate length.