GaN-on-Si technology has emerged naturally as an alternative to GaN-on-sapphire — the mainstream technology for LED applications. But today, despite potential cost benefits, the mass adoption of GaN-on-Si technology for LED applications remains unclear, notes market research firm Yole Développement. Most major LED makers have a patenting activity related to GaN-on-Si technology but, so far, few have made it the core of their strategy and technology roadmap. In contrast to the LED industry, Yole expects GaN-on-Si to be widely adopted by power electronics and RF applications because of its lower cost and CMOS compatibility.

The growth of GaN-on-Si substrate was first reported in the early-1970s (T. L. Chu et al., J. Electrochemical Society, Vol. 118, p1200). Since the early 1990s, an increasing number of academics and industrial concerns have been involved in developing the technology. GaN-on-Si is now poised to meet a series of technical challenges. The high lattice mismatch between GaN and silicon results in a high density of defects (specifically, dislocations) in epitaxial layers. The high mismatch in the thermal coefficient of expansion (TCE) between GaN and silicon leads to a large tensile stress during cooling from the growth temperature to room temperature. The tensile stress can cause film cracking and concave bending of the wafer (warpage). These factors combine to make the reduction of both dislocation density and cracking/warpage a challenge.

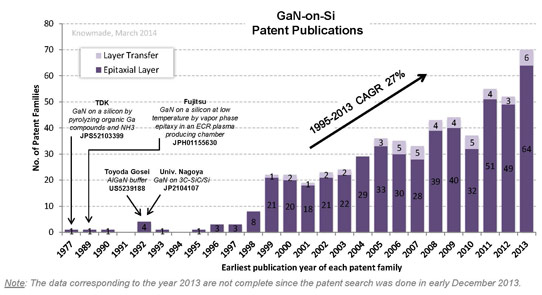

Picture: Time evolution of patent publications (KnowMade, April 2014).

Knowmade's patent investigation covers patents published worldwide up to December 2013. The patents addressing the above-mentioned challenges have been selected, and an in-depth analysis of patent holders and corresponding patented technologies has been conducted. The report does not include patents related to active layers or GaN-based devices.

Fundamental patents describing a GaN-based compound semiconductor grown on a silicon substrate were filed before the 1990s, with the most significant assigned to Japan's TDK and Fujitsu. In the early 1990s, Toyoda Gosei and the University of Nagoya filed the first concepts of a buffer layer for improving GaN crystallinity. Those fundamental patents have been followed by an ever increasing number of applications since 1995 as more companies competed in GaN-on-Si technology to meet the technical challenges and market demand, and to reduce manufacturing costs. Currently, the patented technologies reflect the significant improvements that have been made on key material issues such as dislocation density reduction and stress management for preventing cracking and warpage of the wafer. According to Knowmade's analysis, GaN-on-Si intellectual property (IP) is mature enough to initiate mass production.

Define your patent strategy with deep patent segmentation and a useful database

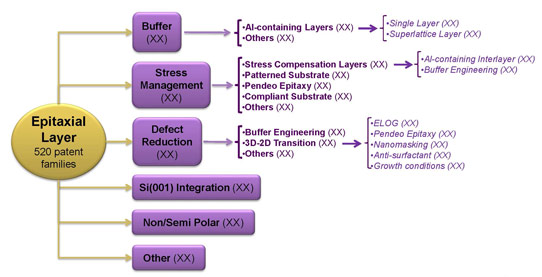

Picture: Breakdown of patent filings by epilayer technology (KnowMade, April 2014).

Knowmade's search strategy combines automated and manual screenings that have led to the selection of more than 560 relevant patent families. Those have been manually segmented by type (epitaxial layer, layer transfer) and organized in various technology segments that are analyzed in detail: defect reduction (ELOG, pendeoepitaxy, nanomasking, defect selective passivation etc), stress management (AlN-based interlayer, buffer engineering, patterned substrate, compliant substrate, etc), and buffer type (Al-containing single layer, compositionally graded AlGaN, superlattices, etc). For each segment, the report provides an analysis including the time evolution of patent filings, and identification of the key players and collaboration networks. More than 60 key patents have been identified on the basis of several indicators (family size, legal status, citations analysis, and impact in GaN-on-Si technology etc).

Key players and new IP challengers

More than 50 companies and academics are involved in GaN-on-Si IP, and most of the major GaN players are present in the list of the top patent applicants. Toyoda Gosei, Toshiba, Panasonic, Mitsubishi, Nitronex, Soitec, and Azzurro have strong IP portfolios related to GaN-based epitaxial layers on silicon, but Samsung, Dowa, LG, Sharp and NGK Insulators are becoming major forces in the GaN-on-Si IP landscape. Soitec and Sumitomo lead in patent filings related to GaN layer transfer onto silicon substrate.

The report provides a ranking and analysis of the relative strengths of the top GaN-on-Si patent holders derived from their portfolio size, patent citations networks, countries of patent filings, and current legal status of patents. Based on this portfolio analysis, Knowmade has identified 15 major players profiled by the report, including a portfolio summary with patenting activity, patented technologies, key patents, granted patents near expiration, partnerships, and IP strength and strategy.

Future of GaN-on-Si IP

Currently, there are just a few players selling either epiwafers or template wafers - or both - on the open market. The number of commercial GaN-on-Si device makers is also limited. Apart from a few noticeable IP collaborations (Nitronex/International Rectifier, Toshiba/Bridgelux, Soitec/Sumitomo, MACOM(Nitronex)/IQE), GaN-on-Si IP has not yet been widely used by companies as leverage to negotiate licensing and supply agreements, says Knowmade. So far, only a few cases of litigation have been observed.

However, the existing IP covers all subjects related to the technical challenges, and the last five years have seen a reinforcement of critical patent filings by major GaN players (Toshiba, Samsung, LG, Sharp, NGK, Sumitomo, Soitec, Azzurro and Dowa). Furthermore, the GaN-on-Si industry is beginning to take shape, as evidenced by the recent interest of RF/power industry players in GaN-on-Si technology (e.g. the acquisition of Nitronex by MACOM) and the desire of several firms to move to the production stage (Toshiba, Samsung etc). An IP battle should hence be expected in the next three years, concludes Knowmade.